### LOGIC DESIGN TESTING.

This thesis is presented to the Kingston Polytechnic and the Council for National Academic Awards for the degree of Doctor of Philosophy

by

A.A. Kaposi, Dipl.Ing.

KP 0220957 8

January 1971.

.

# **IMAGING SERVICES NORTH**

Boston Spa, Wetherby West Yorkshire, LS23 7BQ www.bl.uk

# CONTAINS PULLOUT

Boston Spa, Wetherby West Yorkshire, LS23 7BQ www.bl.uk

# PAGE NUMBERS CLOSE TO THE EDGE OF THE PAGE. SOME ARE CUT OFF

#### ABSTRACT

This thesis concerns the testing of the design of logic networks.

It is shown that conventional test methods, such as hardware testing and computer simulation, fail to satisfy the test requirements of modern logic networks.

A new method is devised, consisting of a series of computer based modular tests, which permit the comprehensive verification of designs.

The feasibility of the new method has been demonstrated on a prototype system.

The work is based on a systems engineering approach which permits viewing the problems of logic design as particular cases of the more general problems of designing large interactive engineering systems. The systems approach also permits the extension of the methods described in this thesis to other areas of engineering.

As part of the thesis, a framework of systems engineering concepts is constructed.

#### ACKNOWLEDGEMENTS

The work described in this thesis was carried out under the supervision of Mr. G. Mayo of the Kingston Polytechnic and of Dr. M.J. Lanigan of the Plessey Company Limited.

The author wishes to acknowledge the contributions of the staff of Plessey Radar Limited, who originated the project and have kept in touch throughout its development; of the staff of the Computer Unit of Kingston Polytechnic for valuable advice and assistance in programming, and to Mr. D.R. Holmes for devising and implementing the prototype system.

Grateful thanks are due to Dr. Lanigan for continued support, guidance and encouragement; to Mr. Mayo for ready help and valuable discussions; to Mr. R.H. Ness and the Directorate of Kingston Polytechnic for providing every facility in the interest of the project.

The course of this work was considerably influenced by the advice of Mr. J.F. Kaposi who scrutinised each stage of its development and by that of Mr. D. Reevski, who suggested the systems approach.

Finally, and most of all, the author is grateful to members of her family whose unfailing patience made the undertaking of such a work possible.

## CONTENTS

ABSTRACT.

ACKNOWLEDGEMENTS.

CONTENTS.

CHAPTER 1. - Background.

CHAPTER 2. - Framework of systems concepts.

CHAPTER 3. - Conventional methods of testing logic design.

CHAPTER 4. - A modular method of testing logic design.

CHAPTER 5. - Organisation of logic design test systems.

CHAPTER 6. - Further developments.

PRINCIPAL REFERENCES.

CHAPTER 1

Background.

#### CHAPTER 1 - BACKGROUND.

In the autumn of 1967 Plessey Radar Limited approached the Kingston Polytechnic (then 'Kingston College of Technology) with the problem of inadequate design reliability of their logic networks. It was thought that the already inadequate design test methods would fail completely when, as a consequence of advancing integrated circuit technology, it will become possible to produce large interactive digital networks as indivisible single components. Thus the management of Plessey Radar Limited requested that the Polytechnic should undertake the development of a method of logic design testing which could satisfy both existing and projected demands.

By the definition of the problem a hardware model of the newly designed network could not always be assumed to be available; thus it was necessary to concentrate upon a computer-based method of solution.

Design testing was seen as a means of generating correct designs. Thus it was thought necessary to construct a design test method which, beyond providing means of comprehensive error detection, also facilitated the correction of these design errors.

Computer simulation was considered as a possible mode of At the time one simulator was generally known and solution. commercially available in this country (36); since then the method has become conventional and has been implemented in some form by numerous industrial and research organisations (for a survey see (1)). These now conventional logic simulators operate upon a computer model of the network by applying a sequence of signal changes to the input terminals and recording the signals appearing at the outputs. This record - a waveform on some suitably designed time scale - contains a part of the required error report in an implicit form. Some of the design errors are not revealed by the test; those detected must be recognised, sorted and classified by the designer upon examination of the output waveforms.

In view of the size and complexity of modern logic networks, the method is considered inadequate. To ensure reliability, a very long sequence of input changes must be originated by the designer; this places extravagant demands on the computer's time, while the very high volume of output data gives an unreasonable task to the designer as a data processor. It is shown in the course of this work that conventional logic simulators appear to raise almost as many problems as they solve. Thus it was thought necessary to search for some alternative method.

The work programme which was proposed for this project in 1968 contained two ideas:

- 1) that simulators should be purpose-built for

- a type of network or for an aspect of performance.

- that care must be taken to use computing facilities efficiently.

This work was divisible into four distinct parts:

- a) problem analysis.

- b) formulation of the principles of solution.

- c) development of techniques of solution.

- design and implementation of a prototype system, proving the feasibility of the principles and techniques.

The work programme isolated the last item of this list, which was subsequently defined as an individual research project (1) and was carried out under the direct financial sponsorship of Plessey Radar Limited. The implementation project ran concurrently with the work described in this thesis and under the supervision of the author.

Detailed problem analysis revealed severe limitations of simulation, even in its unconventional form, as a means of analysis. It was found necessary to have the freedom of choice between alternative modes of analysis. Thus the changed title of this thesis does not contain the word "simulation".

The development of the project was considerably influenced

by a newly emerging interest of a group of people in the Polytechnic in the principles of systems engineering. Common ground was found to exist between projects of seemingly unrelated fields of specialisation and a broadening of outlook permitted useful interchange of ideas between a group of researchers.

In order that logic networks may be placed against a systems engineering background, a framework of consistent concepts and definitions was needed. Since both systems engineering and switching theory are relatively new and rapidly developing subjects, such a framework was not readily available but had to be constructed by adopting existing material, modifying such material, or in many cases, creating new concepts, definitions and terminology. This permitted the viewing of the project against the background of presentday technology and thus it opened the way for the extension of this work to fields outside of logic network analysis. As a consequence, several new research projects have been initiated for members of staff and for post-graduate students (see Chapter 6).

Using the framework of systems engineering, it was possible to propose a model of the design process. Viewing logic network analysis as part of such a procedure, it was found unwise to computerise this part of the process alone. Instead, it seemed desirable to devise methods of automating a larger section of the process, including the assessment of the model performance. The combination of analysis and performance assessment will be termed design testing or verification.

#### CHAPTER 2

#### THE FRAMEWORK OF SYSTEMS CONCEPTS.

2.1 Introduction. 2.2 The concept of a system. 2.2.1 - Behaviour, environment, specifications. 2.2.2 - State. System organisation. 2.3 Resolution. 2.3.1 Structure. 2.3.2 Modelling. 2.4 Modelling the system. 2.4.1 2.4.2 Technique. Classification. 2.4.3 Modelling the environment. 2.4.4 Modelling the state space. 2.4.5 Systems analysis. 2.5 Mode of analysis. 2.5.1 2.5.2 Input data. Input - output mapping. 2.5.3 Resolution, modelling and solution. 2.5.4 Systems design. 2.6

The system is contained within a boundary. The net of all variables outside the boundary which have an effect upon the avera form the <u>setup structurent</u>. The total set of structure the values of the which has a the system environment forms the <u>simplifie formals</u> of the sector.

#### 2.1 - INTRODUCTION.

A system will be described by a model and characterised by its structure and parameters. In this chapter the methods of characterising and analysing systems are discussed and, finally, a model of the systems design process is presented.

#### 2.2 - THE CONCEPT OF A SYSTEM.

#### 2.2.1 - Behaviour, environment, specification.

A system will, in the first instance, be defined as an assembly of objects united by some form of interaction or interdependence. (Note that a more general definition (5) permits a system to contain non-interactive, isolated objects or groups of objects. Systems considered here, which contain no such objects, are defined in (5) as <u>reduced</u> systems). Thus the concept of a system is that of an <u>indivisible entity</u> since all the parts interact and none can be isolated without altering the <u>behaviour</u> of the system; the system concept demands the examination of the overall interaction of a group of objects rather than focussing attention upon the operation of each of the constituent objects in turn.

<u>Behaviour</u> itself is defined as a unique mapping or transformation of inputs (causes) into outputs (effects) and the system will be regarded as the operator performing this transformation. Irrespective of size, appearance, structure or other circumstance of detail, two systems will be regarded as <u>equivalent</u> if their behaviour is identical, that is, if they could be interchanged without altering the relationship between cause and effect.

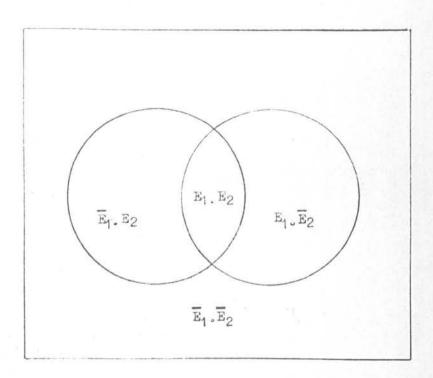

The system is contained within a boundary. The set of all variables outside the boundary which have an effect upon the system form the <u>system environment</u>. The total set of admissible values of the variables of the system environment forms the <u>admissible domain</u> of the system.

The system environment consists of resources which must be available for the operation of the system (sources of energy, manpower, etc.), the physical conditions in which the system operates (such as altitude, temperature, humidity, etc.), the operating signals available to the system and, finally, the loads to which the system provides a service. Henceforward it will be taken for granted that adequate resources are provided at all times; it will also be assumed that the system boundary is drawn in such a way that the load outside this boundary should be constant.

The rest of the environment will have an effect upon the behaviour of the system; all the environmental variables should be considered as inputs of the system.

Let the system have a total of n input variables forming a set  $u_n = \left\{ U_1, U_2, \ldots, U_n \right\}$  and consisting of a set  $u_p$  of p number of physical signals and a set u, of f number of operating sig-The admissible domain of input variables nals or forcing functions. encloses an n-dimensional input space which defines the admissible environment u of the system. Given a system, there is then a set of u of input variables U and a set Z of outputs Z and a transformation F ( ) mapping the inputs into the outputs.

Thus

$$Z = F(u)$$

;

$u_n = \begin{pmatrix} U_1, U_2, \dots & U_n \end{pmatrix}$ ;

$Z = \begin{pmatrix} Z_1, Z_2, \dots & Z_m \end{pmatrix}$  Equation 2.2.1

(see footnote)

for a network of n inputs and m outputs.

FOOTNOTE: Equations, tables and figures will be numbered throughout this thesis by assigning to the first digit the chapter number, to the second digit the section number within the chapter and to the third digit a serial number within the section.

2.2

2.1

This transformation will, in the first instance, define the behaviour of the system.

The formal statement of the system behaviour, together with the definition of the admissible environment, will be a form of <u>system specification</u>. The system specification will thus contain the description of the domain of physical variables, and the domain of operating signals. It will also contain the definition (stochastic or deterministic) of the expected system transformation.

#### 2.2.2 - State.

When defining the system as the transformation Z = F(u), it was tacitly assumed that the system was created at  $t = -\infty$  and that the history of the system had been retained for all time t up to the time of observation. If this assumption is not valid and the inputs are only known <u>after</u> a given instant t<sub>o</sub>, then the history of the inputs previous to t<sub>o</sub> will have some effect upon the system. The accumulation of these effects over the interval  $-\infty \le t \le t_o$  is called the <u>initial state</u> or the <u>state</u> of the system at  $t = t_o$ . Thus the state is defined as a set of time functions s (t) such that if the input set is known for all  $t \le t_o$ , then the knowledge of s (t<sub>o</sub>) is sufficient to determine uniquely the output set Z(t) for all  $t \ge t_o$ .

With the aid of this definition, equation 2.2.1 can be re-written in an equally general but more useful form:

$\Xi (t) = G (u (t), s (t_0)); u = \left\{ U_1, U_2, \dots U_n \right\}; \Xi = \left( \Xi_1, \Xi_2, \dots \Xi_m \right);$  $s = \left\{ S_1, S_2, \dots S_q \right\}$ Equation 2.2.2

for a system of n inputs, m outputs and q states.

Although it is often advantageous to prepare abstract models of systems such that S should be an empty set, physically realisable systems always possess state. Thus, in general, the knowledge of the state of the system is necessary at all time  $t \ge t_0$ . <u>The system</u> <u>equation</u> will consist of the output equation which specifies the behaviour and the <u>state equation</u> which permits the computation of the system state at a time  $t \ge t_o$ .

The general form of the state equation (7) gives the state at time t as

$s(t_1) = H(u(t_0, t_1), s(t_0))$ .... Equation 2.2.3 Here  $u(t_0, t_1)$  expresses the input segment over the time interval  $(t_0, t_1)$ .

A particular form of this equation will be presented in Chapter 4 as the state equation of logical networks.

The concept of state permits the definition of two useful properties of a system (6):

a) Controllability (see also Connectedness, Chapter 4)

The component  $S_i$  (t) of the state  $s = \{S_j\}, j = 1, 2, ..., i, ..., i$ , ..., is controllable if there exists an input u (t),  $t > t_o$  to bring any prescribed initial value  $\propto$  of  $S_i$  ( $t_o$ ) to any other prescribed final value  $\beta$  of  $S_i$  (T) in a finite amount of time (T -  $t_o$ ).

If all components of the state s of the system are controllable then the system is termed <u>completely controllable</u>.

b) <u>Observability</u> (see also definition of sequential networks Chapter 4).

The component  $S_i$  (t) of the state  $s = \{S_j\}$  <u>is observable</u> if there is some finite time T for which a knowledge of the response Z (t) over  $t_0 \leq t \leq T$  is sufficient to determine the initial value  $S_i$  (t<sub>0</sub>) when the state equations of the system are known. Thus an observable state can be determined by observations made on the output. If all components of state 5 are observable then the system is called completely observable.

# 2.3 - SYSTEM ORGANISATION.

#### 2.3.1 - Resolution.

By definition, a system is a complex interactive assembly of identifiable objects which themselves may be complex interactive assemblies. Thus, by re-defining the boundary, the objects of a given system may be considered as systems themselves, as the given system might become one of several objects of a larger system. The organisation of a system will be considered as a hierarchical structure of sub-systems.

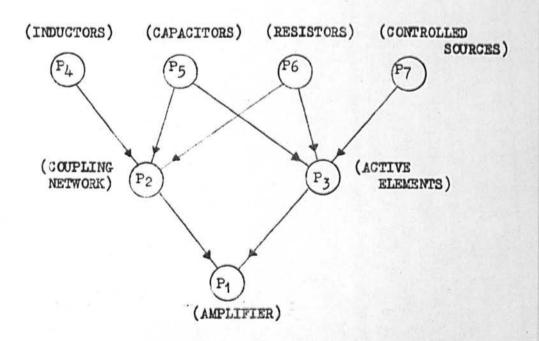

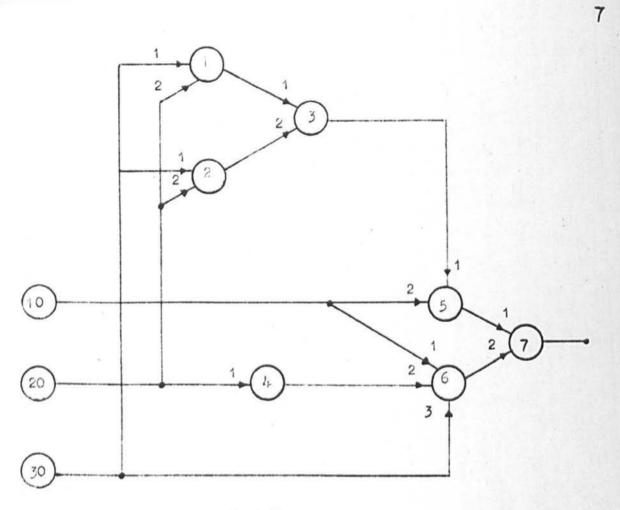

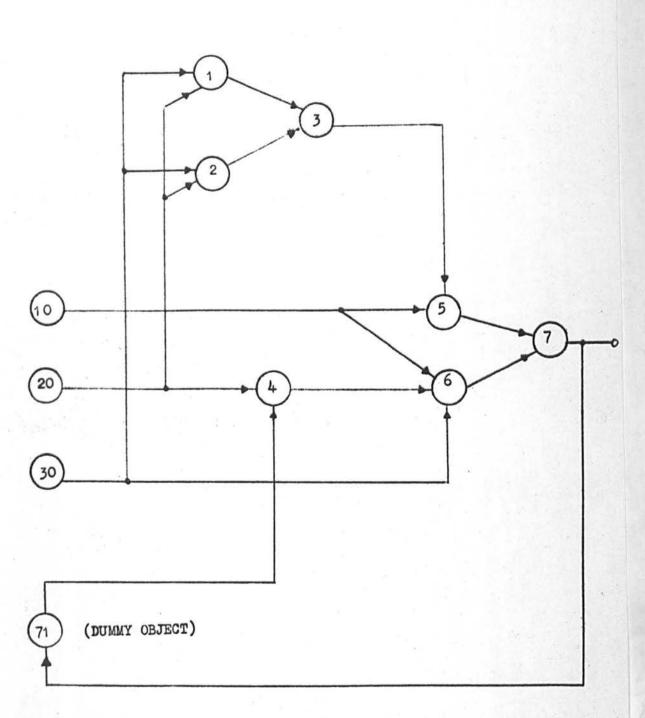

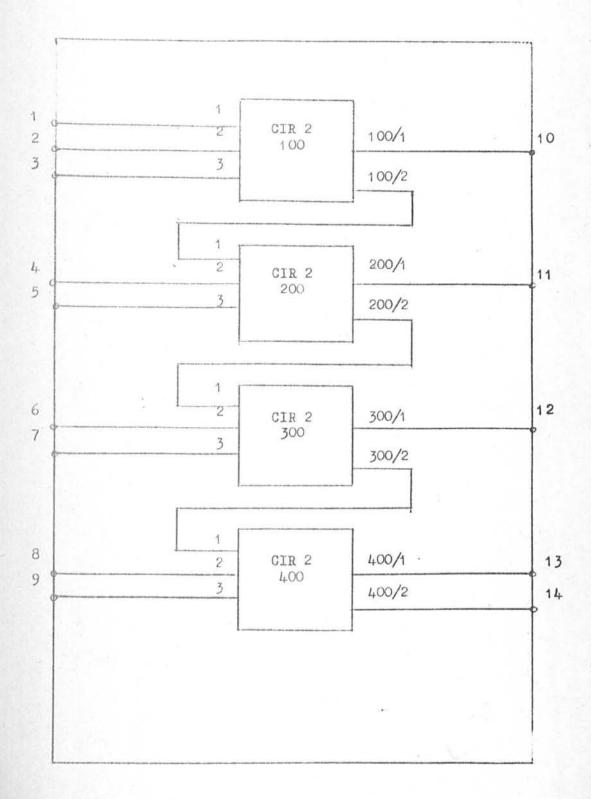

When seeking understanding of a given system, it is frequently necessary to <u>resolve</u> the system to constituent objects. Starting from level 1, when the system P is observed as a whole, the observer may choose to define a number of distinct <u>resolution levels</u> as shown on the <u>resolution graph</u> of Affictitious system (Fig. 2.3.1), suggested by Klir and Valach (5). Each node of this directed graph represents a different system which features as one or more objects of the system at a lower level of resolution. The relationships are simbolized by the arrows; for instance, the system Pl may be constituted of subsystems P2 and P3; the system P7 is the constituent of systems P4, P5 and P6.

As an example, consider the system Pl of Fig. 2.3.1 once again. Assume that P6 needs no detailed examination, i.e. the highest level of resolution will contain the sub-system P6. Pl may now be constituted in a number of different ways:

> of P6, P5 and P2. of P6, P7 and P4. of P6, P4 and P5, etc.

In principle all resolution graphs are "cigar-shaped", with arrows starting from a single point of the common constituent of all sub-systems (the highest level) and terminating on a single point of the total system (the lowest level). The peak of the resolution graph is seldom reached, because of practical reasons; the number of sub-systems constituting the total system increases as the level of resolution increases and it becomes impossible for the designer to consider the interaction between the large number of system objects simultaneously.

Resolution graphs are not unique to a given system; since sub-system boundaries may be drawn in a variety of ways, resolution graphs may also be prepared in a corresponding variety. Consider now the example of Fig. 2.3.2. The selected system is an amplifier, composed of active elements and coupling networks. The equivalent circuit model of active elements and the circuit elements of the coupling networks form further sub-systems. The graph is not continued to higher levels, but it is evidently possible to prepare complex models of each component, accounting for losses, noise, thermal effects, etc., until, ultimately, the graph would reach its peak at a level where sub-systems represent material particles.

It must be noted that this graph offers no insight to the number of objects within the system at each level of resolution, nor to the way in which these objects are interconnected. Information about structure must be presented separately for a given degree of resolution in the form of a graph, table or equivalent.

#### 2.3.2 - Structure.

Let the system be denoted by P and let P, at the selected level of resolution, consist of q number of sub-systems (or system objects). Let the totality of these objects be denoted by D, where the set D is defined as

$D = \{ d_1, d_2, \ldots, d_q \}$

Now let the environment of the system be represented by a "source object" which emits physical and operating signals. Let the source object be denoted by d.

Then the system and its environment will consist of a set of objects  $\boldsymbol{S}$  where

harabaya definition

$$S = \{d_0, d_1, \ldots, d_q\}$$

The <u>structure</u> of the system is defined by the manner in which the elements of the set D are interconnected. Let the symbol  $r_{ij}$  denote the information about the connection of the inputs of object d, to the outputs of object d. Then the set

object d to the outputs of object d. Then the set  $R = \left\{ \begin{array}{c} r_{ij} \end{array} \right\} \quad \text{for all } i, j \quad \text{between l and } q$ will define the system structure at the selected level of resolution.

2.6

The system will now be totally defined by the combination of D and R:

$P = \left\{ D, R \right\}$  .

The structure of the system and its environment will be defined by  $\boldsymbol{\varsigma}$  where

$S = \{r_{i,j}\}$  for all i, j between 0 and q. Denoting the combination of the system and its environment by  $\pi$ ,  $\pi$ will be totally defined by the combination of S and S:

$$\pi = \{ \delta, \varsigma \},$$

Information about the system structure may take such forms as graphs, lists or matrices. For the purpose of this work it was found convenient to adopt the concept of a "structure matrix" and propose its definition as follows:-

Let the system comprise q objects and a source object. Then the structure matrix W will be a square matrix consisting of  $(q + 1)^2$  number of elements. Each element  $W_{ij}$  for all i, j between 0 and q, will be a matrix representing  $r_{ij}$ . If the object dj has "a" number of outputs and the object di has "b" number of inputs then the matrix  $W_{ij}$  will have "a" number of rows and "b" number of columns. Elements of  $W_{ij}$  will be binary numerals showing the presence or absence of a connection between each of the outputs of dj and each of the inputs of di. The matrix  $d_{kk}$  represents the feedback connections between outputs and inputs of the k<sup>th</sup> object of the system.

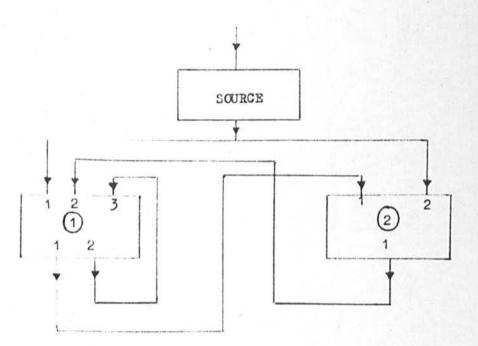

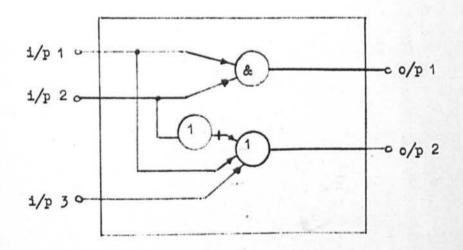

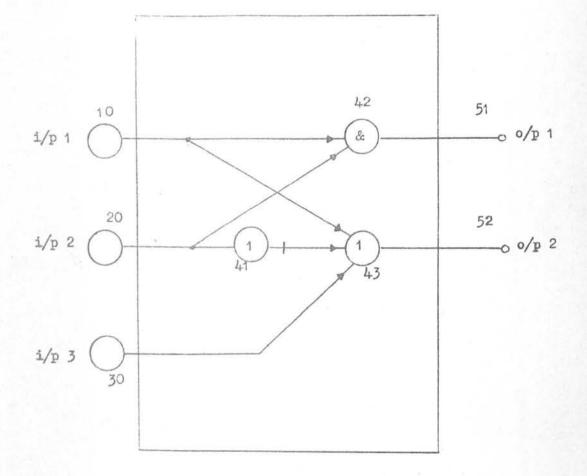

Fig. 2.3.3 shows in graphical form the structure of a system and its environment. As an example of the above definition the structure matrix of the system will now be prepared.

The system comprises q = 2 objects and a source object of a single output and a dummy input. The structure matrix W has  $(q + 1)^2 = 9$  elements as listed below:-

$$\begin{split} \mathbf{W}_{0,0} &= (0) & \mathbf{W}_{0,1} &= (0) & \mathbf{W}_{0,2} &= (0) \\ \mathbf{W}_{1,0} &= (100) & \mathbf{W}_{1,1} &= (000) & \mathbf{W}_{1,2} &= (000) \\ \mathbf{W}_{2,0} &= (001) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,0} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,2} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) & \mathbf{W}_{2,1} &= (000) \\ \mathbf{W}_{2,1} &= (000) & \mathbf$$

The structure matrix W serves no purpose of algebraic manipulation having matrix elements of uneven size. Even so, it is of considerable value since it organises the numerical description of system structure in an easily comprehensible form.

At the cost of some loss of information a more concise version of the structure matrix may be obtained. The <u>coarse structure</u> <u>matrix</u>  $W_c$  will contain a single numeral in the place of each matrix  $W_{ij}$ ; this numeral will be 0 if all elements of  $W_{ij}$  were 0; otherwise it will be 1. The coarse structure matrix indicates the absence or existence of a connection between objects i and j, without specifying the terminals of inter-connection. The coarse structure matrix of the example of Fig 2.3.3 is

$$W_{c} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 1 & 1 \\ 1 & 1 & 0 \end{bmatrix}$$

The first row of W<sub>c</sub> is trivial because the source object, by definition, has no inputs. Consequently the <u>reduced coarse structure</u> matrix W<sub>c</sub> will contain the same information. For the example

$$W_{r} = \begin{bmatrix} 1 & 1 & \overline{1} \\ 1 & 1 & 0 \end{bmatrix}$$

Structure matrices will find wide application in the course of this work.

# 2.4 - MODELLING.

In order to obtain a meaningful definition of the system P it is now necessary to define means for the description of the system objects contained in D. If the behaviour of each object in D could be verbally, numerically, graphically or otherwise described, then the behaviour of the total system could be found by combining this description of object behaviour with information about structure.

Due to the diversity of the ways in which D may be described it is useful to adopt the concept of a model. The <u>model</u> of a system will be defined here as an abstraction of the system, constructed for the purpose of giving insight to the system behaviour.

2.8

It is possible, and sometimes necessary, to construct models of objects of the system at several different resolution levels. Thus, a model may seek to represent the total system or one of its constituents.

Models of engineering systems are usually <u>quantitative</u>. Such quantitative models will be characterised by an ordered set of numerals called the <u>parameters</u> of the system.

It will be useful to extend the concept of a parameter to non-numerical information about a modelled system. Thus a parameter may denote the colour, shape or logical behaviour of an object of the system.

Modelling of engineering systems will consist of

- a) choosing a resolution level, thus defining the boundary of each system object.

- b) characterising the system structure and

- c) defining of object parameters.

#### 2.4.1 - Modelling the system.

Modelling will be described as the procedure of obtaining the model of the system for the purpose of observing the system behaviour.

The model usually represents a simplified version of the system, purposely built to facilitate the observation of a limited set of its features. Thus the <u>specification</u> of a model would consist of the specification of

- a) the set of characteristics of the system which are to be observed and

- b) the accuracy with which these characteristics are to be described.

The <u>quality</u> of the model will be defined here by an objective function, taking account of the extent to which the model meets the specifications, the cost of building the model and the facility of it's use. There is no improvement in quality associated with exceeding the model specifications and since the simplest model is usually easiest to use, this will represent the model of optimum quality. However, the use of complex models is justified when they are flexible and can be used for more than one purpose. Such multi-purpose models share the cost of development between a number of applications and thus acquire higher quality rating, but, since such models depend for their quality upon the need for all applications, they are very sensitive to modifications of the analysis process.

It is usually easier to maintain the quality of models by constructing a modelling sequence which relies upon a sequence of modifications (usually refinements). In this case a model is purposebuilt for each application, thus is optimally easy to use, but it is built upon the foundation of another model, used earlier in the process, thus the cost consists of a relatively small increment. Process modification affects the incremental cost only. Sequential modelling will find application in the course of this work.

#### 2.4.2 - Technique.

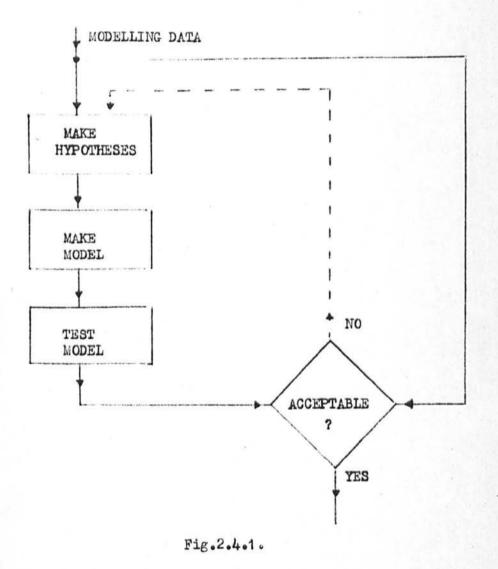

The technique of modelling is shown schematically on Fig.2.4.1. The modelling data is the basis upon which the hypothesis is set up. When the model is constructed and tested the modelling data is used again as the basis of assessment.

If serial modelling is used, as recommended in section 2.4.1, the process is repeated several times, taking into account an increasing detail of modelling data. Thus a comprehensive model is built by a series of approximations.

#### 2.4.3 - Classification.

Several criteria have been suggested for the classification of models (5), (9), (10), (12). Without further comment some grounds for classification are listed here, taken mainly from Chestunt (11). 1) Language.

- a) Verbal models

- b) Iconic models (maps, photographs, etc.)

- c) Symbolic models (flow charts, logic diagrams, etc.)

- d) Analogue models

- e) Physical models.

#### 2) Method of solution

- a) Analytic models

- b) Numerical deterministic models

- c) Numerical stochastic models.

#### 3) Resemblance to reality

- a) Isomorphic models

- b) Homomorphic models

- c) Abstract models.

Such formal classifications have been found helpful in understanding the problems of modelling logical networks.

#### 2.4.4 - Modelling the environment.

It is possible to extend the concept of a model to the environment itself. If a suitable model is found to represent, in some abstract form, the source object  $d_0$ , then the objects of  $\delta$ are all modelled and can be observed. This use of the concept of a model is considered both advantageous and novel.

In this section the environment of a system will first be examined; secondly, the problems of modelling the environment will be discussed.

Let the source object  $d_0$  have n number of output terminals. This means that the system P is operating in an n-dimensional input space which is composed of operating signals and physical signals. The boundary of this space is given in the specification of the admissible domain.

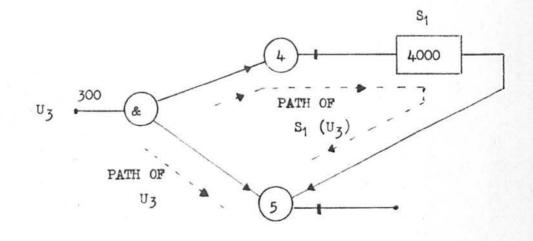

A verbal model of the source object is now proposed. Let the signal at the i<sup>th</sup> output terminal of the source object be given by some quantity  $U_i$  ( $t_0$ ) at the instant  $t_0$ . Then the totality of  $U_i$  ( $t_0$ ) for all i between 1 and n defines a point Y in n-dimensional space within the admissible domain. The behaviour of the source object in the interval  $\tau = t_1 - t_0$  will now be pictured as the parameters in n dimensions of the moving point Y. In the course of normal operation point  $\succ$  may travel on some path X where X is usually a continuous line.

Let the purpose of an observer be now to obtain information about the system behaviour. The observer may now follow the variations of the system outputs as functions of the path of point  $\checkmark$ . This procedure leads to frustration because the point  $\checkmark$  may stop moving for periods or may keep returning to routes already covered, missing interesting areas altogether. It appears advantageous to replace the real-world source object with another which is under the observer's control. If the substitution is sufficiently ingenious then the observer may regulate the route X according to his own purpose.

Let the purpose of the observer be re-defined: information is to be collected about the total range of system behaviour. With the aid of the verbal model of the source object it is easy to see that it is impossible to achieve this purpose: the point  $\checkmark$  will never touch all of the points of the space because the number of points is an n-dimensional infinity.

Let the purpose of the observer be re-defined once more: information is to be collected about the system behaviour in such a way that it should become possible to predict the system behaviour by the use of this information at any point within the admissible domain.

This objective is reasonable. It is defined here as the objective of systems analysis.

To demonstrate one way of meeting this objective, let the verbal model of the source object be changed. Instead of the continuous n-dimensional space in which  $\checkmark$  may move, consider now the same space in which a finite number of points N are strategically placed. The movement of  $\checkmark$  will now be discontinuous, jumping from point to point. The total space may be covered by N number of changes in the position of the point  $\checkmark$  This model of the source object may be translated into numerical form: each of the N number of points can be given by a set of n numerals. The behaviour of the source object may now be given in form of a table which has one column for giving the instances of time when the position of Y changes, and n more columns describing each of the co-ordinates of Y. The observer will achieve his purpose by first covering all of the N points of the space and then, if necessary, interpolating between them to calculate the behaviour at an intermediate point. (see footnote).

The concept of an environmental model has found extensive use in Chapters 3 and 4 of this thesis.

## 2.4.5 - Modelling the state space.

As seen earlier (section 2.2.2) systems in general possess state. In the course of modelling the objects within the set D, it may have been decided to compile an analytic model of the system which would allow the description of the state in terms of m number of state variables. When the behaviour of the system is observed, the system may be anywhere in this m-dimensional state space and therefore the results can only be interpreted un-ambiguously if the initial state of the system is known.

Let the observer have a new and ambitious purpose of collecting information about the system behaviour in such a way that estimate could be made of the behaviour irrespective of the initial state of the system. This means that tests must be conducted to cover the total state space.

The task is impossible. At the outset, the moving point Y may be anywhere in an m-dimensional infinite number of points. Evidently it is necessary to quantise this area in the same way as in the case of the n-dimensional input space, permitting now a finite M number of points for the purposes of testing. Combining the

FOOTNOTE: This procedure will be shown as valid only for systems without state.

m-dimensional state space with its M points with the n-dimensional input space with its N points, a total space of q = (n + m)dimensions may be perceived, consisting of both state variables and input variables, in which  $Q = N \ge M$  number of points are defined for the moving point  $\succ$ .

The ingenious observer may succeed in constructing a source model in such a way that direct control is maintained over each of the n input parameters. The parameters of state space however are not usually directly controllable. Referring to the definition of controllability, it will be seen that systems which are not completely controllable can never be induced to occupy certain areas of the state space. Consequently no physical model of such a system will permit the scanning of the total q-dimensional sample space.

One of the merits of the method of design verification proposed in this work is that it permits the designer the direct control of all variables of the sample space, as will be seen in chapter 4.

#### 2.5 - SYSTEMS ANALYSIS.

Systems analysis will be defined as the process of obtaining information about the behaviour of the system in order to satisfy the objective set up in section 2.4.4. The purpose of analysis is to serve design verification, as defined in section 2.6.1.

The analysis process will be termed <u>comprehensive</u> if it gives deterministic information about the system behaviour at any point within the boundary of the admissible environment.

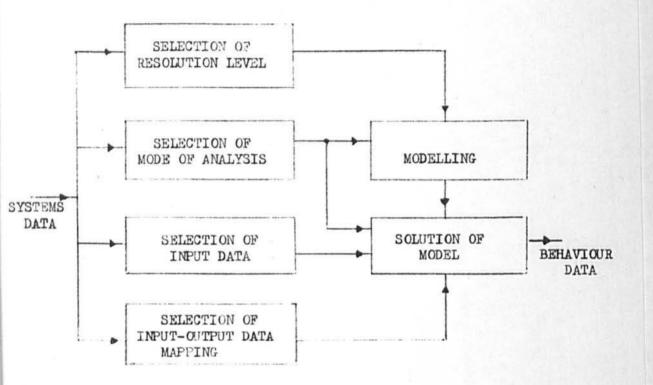

Fig. 2.5.1 shows a model of the systems analysis process. The model attempts to be general and therefore contains some parts which will be found irrelevant for certain modes of analysis. At the same time the model aims for simplicity and does not show all of the connections between parts of the model which may be required in the course of a given analysis process.

#### 2.5.1 - Modes of analysis.

Depending upon the relationship of the real-world system

and its environment to the test system and its environment, the analysis will be said to be conducted in one of several possible modes.

Five different modes of analysis are suggested and defined by Blumstein (2) as reported by Deutsch (3). This classification was found in-complete and the definitions somewhat ambiguous. Therefore, with the aid of Gordon's definition of simulation (4) six modes of analysis will be defined for the purpose of this work:

- Real-world analysis observation of the realworld system in its natural environment. In this case the real-world system is identical to the test system and the real-world environment acts as the test environment.

- Operational exercise observation of the realworld system in a test environment which has properties similar to the real-world environment.

- 3) Gaming the test system is a hybrid, comprising a selection of real-world sub-systems and subsystem models; the test environment is similar to the real-world environment.

- Simulation observation over time of a model of a system in a simulated environment.

- 5) Analytical testing solution of equations which represent the test system and the test environment in symbolic form.

- 6) Numerical testing solution of numberical model of the test system without direct reference to the time domain.

Deutsch (3) remarks that the modes of analysis are numbered so that higher-order modes re-present increasing distances from reality. While this is undoubtedly true, choosing one of the higher order modes of analysis does not necessarily imply loss of information about the system behaviour. On the contrary, examples will be found in the course of this work where high-order modes provide information not available by lower order modes of analysis. It will be observed that the definition of simulation used here contains no reference to the tools of analysis: simulation may be performed on a physical model or on a computer model, so long as direct reference is maintained to the time domain. The time scale may be identical to that of the real system, or trivial mapping of inputs and outputs may be used.

#### 2.5.2 - Input data.

Let the purpose of the designer be to analyse a system comprehensively. The question is now: how should the test data be designed to make such analysis possible.

The task is evidently impossible unless a quantised model of the source object is acceptable. Let it therefore be assumed that such a model has been found and that it contains Q number of points. The analysis will now need to investigate both the steady-state and transient behaviour of the system.

If the system may be assumed completely controllable and unconditionally stable then it is theoretically possible to test the steady-state response in each of the Q points. In addition, the transient response needs to be recorded by changing each of the Q points under the influence of all the input variables.

Designing a test sequence which would allow all these tests and which is/for a system or its physical model is a task of extreme difficulty. Furthermore, the process would usually be found extravagant in terms of testing time and cost. Therefore, comprehensive analysis, even in terms of quantised source models, is seldom attempted. Instead, systems are either randomly tested (i.e. subjected to a random sequence of environmental changes) or, more frequently, tested in terms of a sequence of test data, which is judged to be of particular significance or relevance. The latter practice is dangerous since it is open to the value judgement of the designer whose work the analysis seeks to test (see also Chapter 3).

The test method proposed in the course of this work was designed with particular reference to the problems of test data generation.

#### 2.5.3 - Input - output mapping.

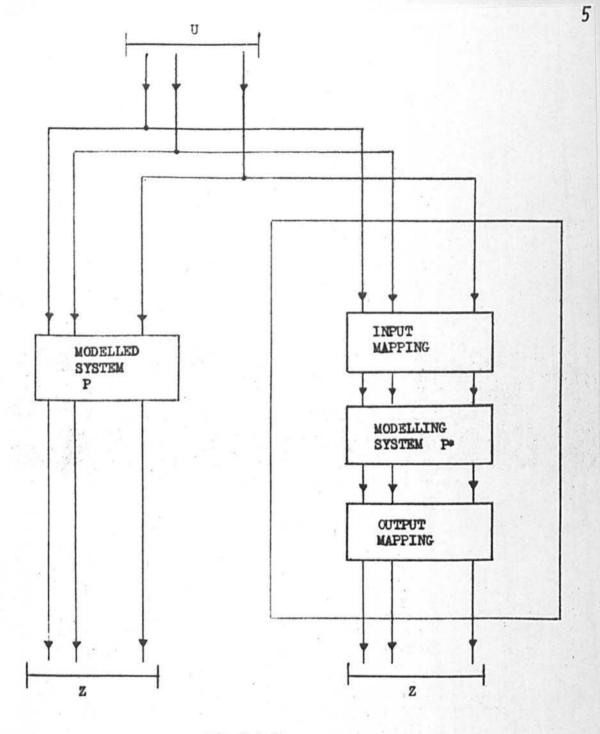

Fig. 2.5.2 shows two ways in which the behaviour of a system may be observed. The direct method on the left corresponds to the lowest mode of analysis. All higher order modes demand that a model of the system under observation be available. In all these cases the real-world signals of input and output require suitable interpretation or mapping.

The mapping of inputs and outputs may be a trivial isomorphic transformation such as scaling, creating analogue signals in new physical dimensions or representing a signal as data in a computer and recovering the output by mapping of the printout. On the other hand, mapping may involve a transformation which changes the mathematical relationship between the systems attributes without affecting the system behaviour. One example is the change from time-domain to frequency domain for the analysis of electrical systems; the inverse transformation re-constitutes the outputs in the time domain. Another example, drawn from the context of logic network analysis, may be the derivation of a truth table or DIRECTORY by a parallel processing procedure (see chapter 4). In this case input variations are mapped into a designation number and the total input domain is covered by a single analysis run through the network. The output is mapped into The result can then be interpreted in terms of time-varying a table. input signals to which the response is available.

# 2.5.4 - Resolution, modelling and solution.

All but the two kwest-order modes of analysis call for some form of a system model. Before embarking upon a modelling procedure it is necessary to define the level to which the system may be resolved. This choice of resolution level determines the boundary around objects comprising the system.

In the course of analysis of a complex system it may be necessary or opportune to re -define the boundary several times. For instance, in the course of analysing a transistor amplifier, the circuit may, at first, be considered as a d.c. network, stationary at the operating point; then, in subsequent stages of analysis, the model of each component may be resolved to higher levels, <u>increasing</u> the information about the network.

It is also possible to envisage a process of analysis involving the gradual reduction of resolution level. Taking the example of logical networks, after detailed analysis of a non-linear network designed to act as a set of logical gates, it will be found advantageous to move to a lower level and consider the gate as the smallest object in a larger network; then again, after analysis, the large network may be regarded as the smallest object of the over-all system which was the original concern of the analysis process.

The purpose of reducing the resolution level is to reduce the modelling data. The new homomorphic model contains less information than the higher-level model, due to the fact that some <u>simplifying</u> <u>assumptions</u> have been accepted which permit the omission of a certain amount of detail.

Solution may consist of application of test data and observation of outputs, or application of test data and computation of outputs, or again, solution of equations and substitution of test data. In addition, some analysis procedures will be found to solve their models by observation and without any reference to test data. Due to the problems of test data generation discussed earlier in this chapter, these latter methods are particularly attractive and have been given attention in the course of this work.

#### 2.6 - SYSTEMS DESIGN.

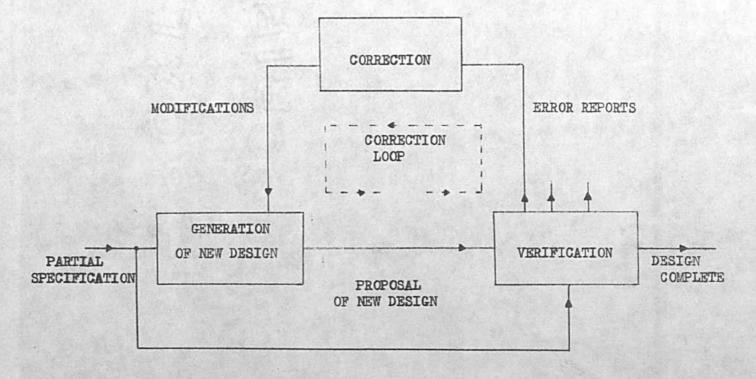

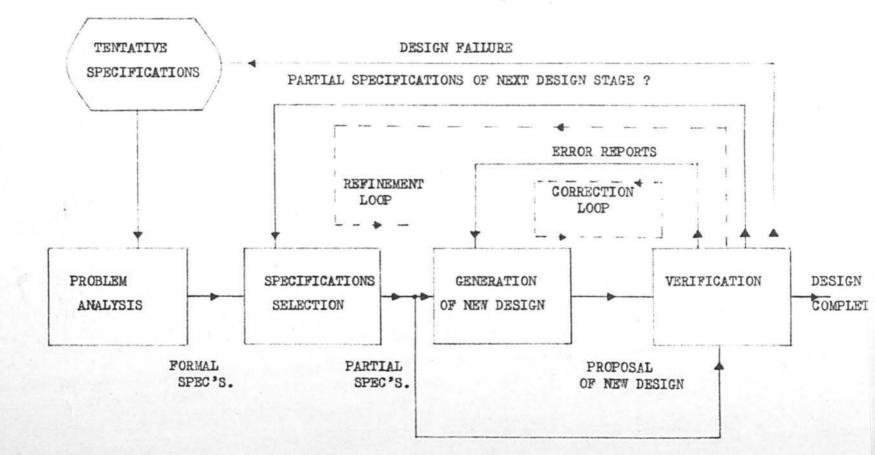

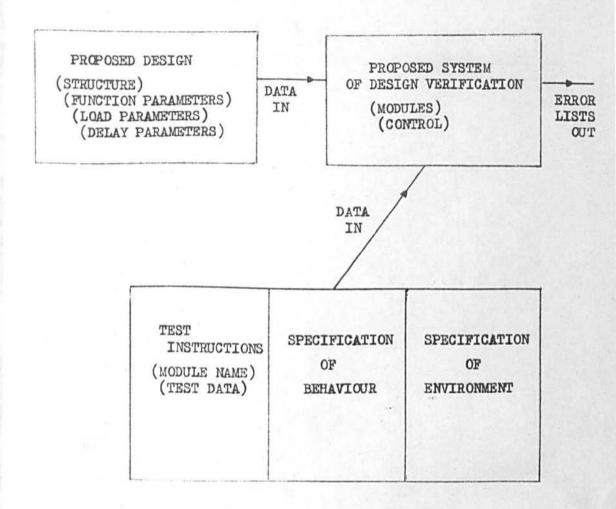

A model of the design process will now be proposed and discussed with reference to Fig. 2.6.1.

It will be assumed that some demand exists which must be satisfied by creating a new engineering system. A statement must be available which will <u>specify</u> the required behaviour and the admissible environment of the new system. This statement is called the tentative specification of the system.

The first task of the system designer will be termed <u>problem analysis</u>, which consists of the examination of the feasibility and completeness of the specifications. Specifications will be called <u>non-feasible</u> if they contain contradictary demands and <u>incomplete</u> if they do not describe the environment or behaviour uniquely. In the course of problem analysis the designer will initiate the amendment of non-feasible specifications. He will also investigate whether incompleteness is intentional or not. He will utilise the freedom afforded by intentional incompleteness at a later stage of the design process for the optimisation of some parameters not included in the specifications.

As an outcome of problem analysis the behaviour - and environmental specifications are formalised and the next stage of the design process may commence.

The designer's main function is to generate proposals for the new design. This task is usually so complex that it is carried out in a sequence of stages of refinements which represent successive approximations of the specification. Each stage of approximation operates upon a restricted version of the specifications (termed the <u>partial</u> specifications) which the designer must individually select for each stage.

Assuming now that suitable partial specifications are available, a version of the design must be proposed which will fulfil those specifications. At the present time the designer must rely almost entirely upon intuitive or evolutionary methods of design generation: formal synthesis procedures are only available in a very limited field of engineering and they only operate under severely restricted environmental conditions. Logic design is better served by synthesis techniques than other engineering fields; even so, current practice must rely to a large extent upon the **inventiveness** of the designer. The proposal of the new design is a model of the system under development. This model must now be <u>analysed</u> and its behaviour assessed against the partial specifications. The combination of analysis and assessment will be termed <u>verification</u> or design testing.

The purpose of design verification is to provide conclusive answers to questions which are implicit in the partial specifications. A sample list of design verification questions is shown here:

- 1) Is the performance of the new design correct, given normal environment and nominal component values?

- 2) How sensitive is the performance to expected changes in environment and component values?

- 3) If subjected to unusual environmental conditions, would the new design fail catastrophically?

If verification detects design errors, these must be used to stimulate design modification. Alternatively, the error reports may be interpreted as indications of unrealistic tentative specifications. In the latter case the design process fails completely and new tentative specifications must be set up or the project cancelled.

Assuming now an error report which does not lead to design failure, the new design is gradually corrected (correction loop, Fig. 2.6.1) until verification succeeds. Now the next stage of design refinement may be entered and new partial specifications are requested by way of the refinement loop (Fig. 2.6.1).

The iterative design process is complete when all aspects of the formal specifications have been taken into account and verification has been successful.

2.20

### CHAPTER 3

## CONVENTIONAL METHODS OF TESTING LOGIC DESIGN.

| 3.1 | - | Introduction. |                                        |

|-----|---|---------------|----------------------------------------|

|     |   | 3.1.1         | - Objectives.                          |

| 3.2 | - | Hardwar       | re methods of design testing.          |

|     |   | 3.2.1         | - Mode of analysis.                    |

|     |   | 3.2.2         | - Resolution level.                    |

|     |   | 3.2.3         | - Modelling.                           |

|     |   | 3.2.4         | - Inputs.                              |

|     |   | 3.2.5         | - Solution and Assessment.             |

|     |   | 3.2.6         | - Conclusions.                         |

| 3.3 |   | Design        | testing by computer simulation.        |

|     |   | 3.3.1         | - Resolution.                          |

|     |   | 3.3.2         | - Modelling.                           |

|     |   | 3.3.3         | - Inputs.                              |

|     |   | 3.3.4         | - Input - output mapping.              |

|     |   | 3.3.5         | - Solution and Assessment.             |

| 3.4 | - |               | testing by higher-order modes of vsis. |

#### 3.1 - INTRODUCTION.

This chapter presents a survey of logic design verification methods in current use and aims to show that these methods fail to satisfy current demands of modern integrated circuit devices or complex logical systems.

The shortcomings of conventional methods are carefully noted. The newly proposed method, described in Chapter 4, seeks to eliminate or, at any rate, minimise the problems uncovered in the course of this survey.

With reference to the available repertoire of modes of analysis (section 2.5.1), analysis techniques of current use will be found to fall into the classes of Operational Exercise, Gaming, Simulation, Analytical Testing and Numerical Testing, with overwhelming emphasis on Simulation.

#### 3.1.1 - Objective.

The purpose of logic network analysis is to serve the process of design verification. In turn, the purpose of design verification is to answer specific questions the designer raises about the new design (see 2.6). Consequently, the operational objectives of systems analysis can be formulated as follows:

- a) to collect information about the performance of the new design,

- b) to present this information in a form convenient for performance assessment,

- c) to operate fast, cheaply and reliably.

The analysis techniques discussed in this chapter will be evaluated against these objectives.

<u>3.2 - HARDWARE METHODS OF DESIGN TESTING.</u> <u>3.2.1 - Mode of analysis.</u>

The traditional way of verifying the design of a logical network is to build the total system of the proposed design in a form resembling the real-world system and subject this to a simulated environment. The data resulting from the analysis is then compared with the specification.

The technique in this form amounts to Operational Exercise and is frequently applied to small logical networks.

In the case of more complex networks it is customary to examine the performance of sub-networks before the system is finally assembled. The phase of sub-system testing is perhaps best classified as Gaming, because the real-world model of the sub-system under test is usually surrounded by models simulating the effect of the rest of the system.

If such systems are mass-produced, then the design verification uses a model which may have no object in common with any system on the production line. The mode of analysis is Simulation - the only mode of analysis appropriate to hardware testing of complex networks.

#### 3.2.2 - Resolution level.

At the time of discrete-component hardware technology, designers had almost unlimited freedom of choice of resolution levels during analysis; it was possible to commence simulation by regarding the system as a whole; at the event of the first failure the design engineer could gradually elevate the resolution until the level of a single electrical component was reached. The procedure gave a sense of satisfaction to an engineer who could correct the design error on the spot; however, it was failing by all the analysis objectives as would any other procedure which allows the handling of too many individual objects. The search for the location, appearance, connections and signals of several hundred error-prone individual components could not be condoned. Thus, well before the advent of integrated circuit technology, networks of modular and hierarchical structure were constructed, allowing no more than two different resolution levels for each test and no more than a few dozen individual objects and monitoring points.

Design testing of a hierarchical system proceeds in a sequence of stages. First, the design of the smallest module(s)

is verified. If these are constructed of discrete components then it is possible to ascend to the level of single component.

When testing the design of a module at the next level of hierarchy then it is necessary to be able to assume all small modules as perfect (verified by the previous test) and indivisible. If this assumption can not be made then, in order to locate and correct the error, the resolution level must be increased, demolishing the boundary of the previously tested module. The difficulty and confusion can obviously be avoided by testing the small module reliably in the first place, as demanded by objective c). This demand for reliability becomes more pressing as the size of the system and the number of hierarchical levels increase.

#### 3.2.3 - Modelling.

The analysis of logical networks by hardware simulation demands that a hardware model be constructed of the real-world system which will be subjected to time-variant signals. The modelling process itself appears to be a trivial exercise of constructing a physical model by use of components like those of the real-life system. In practice however the problems associated with modelling prove far from trivial: due to component tolerances and differences in physical layout, the <u>correlation</u> between the performance of the model and that of the real-world system is in doubt. Thus the information collected during analysis fails to represent reliably the performance of the real-world system, thus failing to satisfy the objectives of analysis.

Designers seek to remedy this situation in two ways:

by increasing the sample size, i.e. analysing several models, built of randomly selected components.

While improving reliability, the method increases the volume of data, the cost and time of analysis and raises the new problem of statistical assessment of results.

3.3

2) by evaluating the expected extreme in component values and selecting the components of the model so as to represent the "worst case" in system behaviour. The model thus permits the assignment of a boundary to the expected system behaviour.

If the estimate of "worst case" is correct then the method satisfies all the objectives listed; however, the resulting design is unnecessarily expensive.

This second solution is obviously only available in case of use of discrete-component hardware: users of integrated circuit hardware have very little information about the expected behaviour of components and no information at all about the extremes of acceptable performance. Even if this information should be available, the task of selecting worst-case items of multiple-function integrated circuit devices is formidable - worst-case assessment seems completely impractical.

Attempts have been made to build worst-case discretecomponent models of integrated circuit devices. These have been proven unsuccessful due to the poor correlation between system and model behaviour. Some designers tried to construct a sophisticated discrete-component model, using time scaling to reconstruct the wavelength of signals in integrated circuit devices. This method is too complicated and the results are far too sensitive to scaling factors to be reliable.

The mounting problems of modelling integrated circuit devices must be viewed against the increasing demands for design verification: the tooling costs for a single component are the same as for massproduced article and, due to the magnitude of this cost, design errors can not be tolerated.

Hardware test methods offer no satisfactory solution to the modelling problem of integrated circuit devices. Reluctant designers are forced to seek computer solutions to their problems.

## 3.2.4 - Inputs.

When a hardware model is constructed, the designer subjects this to simulation, observes the output and verifies the design. If the system has n operating signals, m physical signals and q state variables then the sample space has an (n + m + q) - dimensional infinite number of points (see sections 2.4.4 and 2.4.5).

To attempt comprehensive analysis, it is necessary to devise some suitable discrete model of this sample space. However, unless the system is known to be completely controllable (see Chapter 2) it is not possible to scan the total sample space in a finite amount of time. In the case of completely controllable systems the problem is theoretically accessible but practically unsupportable, since the number of input changes necessary for comprehensive steady-state and transient testing is excessive for all but the most trivial of systems.

In current practice the job of design verification is conducted at a few points of the sample space, under conditions the designer considers representative or critical. If the design fails these tests then it is evidently in need of modification. If it passes the tests then it may still contain numerous errors and may fail in service. Design errors in computers often come to light years after machines are installed, indicating that a compromise has been selected between the conflicting objectives for speedy, low-cost and reliable analysis.

It is suggested here that the problems arising from the vastness of the number of points of the sample space are akin to those arising from the vastness of the number of components comprising a complex system. The solution of the sample-space problem might be sought along the same lines as that of hardware: it could be decided that there is a maximum number of points of sample space one can efficiently handle; therefore models of inputs must be so constructed as to fit within this number. Input signals may thus be "modularly" modelled and as the number of signals increases so the resolution must reduce to keep down the number of points of the sample space.

According to this principle, it will be reasonable to consider the effects of physical signals, rise-and-fall times and signal level variations when testing a single logical gate, but unreasonable to resolve input signals to more than two voltage levels when testing a complex gate assembly. In the latter case it would be necessary to form a model of the objects of the assembly which accounts for the effects of the neglected signals.

Unfortunately for logic designers, the number of points of sample space increases very fast with the number of input variables and the reduction of detail of input signals can not keep pace with this increase. Thus the computer simulation methods discussed later in this chapter merely manage to provide a temporary solution by increasing the speed of simulation. Ultimately the failure of simulation as a means of analysis must be faced.

### 3.2.5 - Solution and assessment.

Let it now be assumed that a satisfactory set of test conditions has been compiled and the model is subjected to these tests. The result of the analysis is available in the form of a set of output waveforms. These waveforms must now be observed or recorded and assessed against some form of records of the performance specifications.

The traditional instrument of recording, offering the advantage of familiarity, is the oscilloscope. Against this must be set numerous disadvantages: the number of channels is limited, thus, to observe the correlation of several waveforms, tests must be repeated, or more than one oscilloscope used; signals must be repetitively applied to permit observation; the standard signals can not be displayed - the real-world system does not exist - hence the oscillogram must be compared with a waveform or table by eye, or else recorded as a waveform or table.

The instrument of assessment is the design engineer who often represents the weakest link in the chain of the verification

process. Human error is mainly due to the repetitiveness of the task of assessment and the inefficiency of men to handle the large volumes of data necessary for reliable analysis.

# 3.2.6 - Conclusions.

Hardware testing of the design of logical systems is, at best, limited to small systems; at worst it is an unqualified failure. The method fails completely in terms of complex integrated circuit devices which, due to their high initial manufacturing costs, demand reliable design verification. As advances in technology permit the increase of the complexity of these devices and enhanced their prominence among other forms of hardware, the development of alternative forms of design testing become imperative. Thus, almost simultaneously, several computer simulators have been developed by device manufacturers, instrument manufacturers and research institutions, seeking to provide a solution to the problems unsolved by hardware testing.

# 3.3 - DESIGN TESTING BY COMPUTER

## SIMULATION.

The preparation of a comparative survey of logic simulators does not fall within the scope of this work. Such a survey, examining the features, facilities, techniques and relative merits of available simulators, will be presented in the thesis concerning the development of a prototype system (1). Instead, this section will attempt to assess the potential of logic simulation as a tool of logic design verification. In the course of discussion references will be made to some of the logic simulators in current use, illustrating some of their features and facilities.

## 3.3.1 - Resolution.

At the highest level of resolution, used by any of the known logic simulators, stands the single logical gate. It is thus assumed that the system under test consists of objects which represent Boolean operators and the simplest functional object to which the system can be divided operates as a simple logical connective. The standard repertoire of gate functions is AND, OR, NOT, with associated delays (see Modelling). Some simulators extend the range of gate functions to NAND and NOR.

A group of simulators, such as the APACE program 'LOCA', the Plessey DA70 and the Siemens 'DICAP', demand that systems under test be always resolved to such a high level; thus designers must code their networks by use of a fixed library of standard elements.

The advantage of systems using this fixed resolution level lies in the simplicity of the programs. The disadvantages are measurable in terms of coding time and coding error: the designer must repeatedly declare each gate within each standard hardware subsystem, multiplying the coding time and committing a multiplicity of errors. An additional disadvantage is, that the computer must repeatedly analyse standard hardware sub-systems within the system. Thus it is suggested that simulators with fixed resolution level are only suitable for the analysis of small systems.

A second group of programs to which the Norwegian program "LOGIC" and the Elliott "LASS" belong, also fixes the resolution level but permits an expandable library of standard objects. When the computer model of the network is constructed, each object is checked against the current library list. Unrecognised objects are reported as program errors. Standard groups of gate elements can be entered in the library as standard objects by giving them a unique name and describing them by a sub-routine, (21), (22). The use of this method is demonstrated in (21), where flipflops are "modelled" and their functional description is entered in the library as a standard "logic rule".

These facilities, as provided in 'LOGIC', replace the whole of a sub-system by a sub-routine. The sub-routine represents a terminal model of the perfect sub-system; consequently care must be exercised in verifying the design of a sub-system before replacing it by the sub-routine. If reliable sub-system testing may be assumed then this method satisfies the objectives by reducing both the time

of coding and the time of computation. The limitations of such subroutine models of sub-systems will be discussed in the section dealing with Modelling.

The third group of programs to which the Racal "REDAF 22" and the Fairchild "FAIRSIM II" belong, permit a flexible choice of resolution levels. It is possible to construct sub-systems of nested modules and the system under analysis may be composed of combinations of single gate objects or of complex nested sub-systems. It is customary to impose a limit to the depth of resolution.

This method gives great help at the stage of modelling, but it in no way assists the analysis by the computer since, before analysis commences, the modular structure is usually broken.down to constituent gate elements and the analysis progresses from gate to gate.

#### 3.3.2 - Modelling.

Simulators differ greatly in the format they use in specifying the objects of the system under test. However, substantially they all refer to four types of data, amounting to the model of an object:

- 1) object identification

- structure the connection of the object to other objects of the system

- 3) functional description.

- 4) timing description.

#### Identification.

Each object is uniquely identified by a code. Information about the object is referenced by this code throughout simulation.

### Structure.

Connection between system objects is specified in one of three ways:

- a) considering the object as a recipient of signals

- b) considering the object as a source of signals.

- c) specifying all the connections to and from a given object. This method duplicates the structure information, thus doubling the coding

time. The redundancy is then used for

diagnosis of coding errors.

## Function.

The functional description assigns to the object one of a set of recognised parameters. Dependent upon the resolution as seen earlier, functions may be simple logical connectives, combinations of simple logical connectives or functions outside of the range of logical functions. The latter may arise by the use of sub-routine models.

It will be appropriate to devote some attention to the principles upon which sub-routine models are based.

Let a sub-system to be modelled consist of a set of logical gates, each representing a simple logical connective. Let this system be subjected to an n-dimensional environment and let it have m number of state variables. Then the terminal model of this system would contain the relationships of

| 2<br>5 | (t)<br>(t) | = = | G<br>H           | ( 1<br>( 1     | (t<br>(t | ),<br>), | s<br>s | (t <sub>0</sub> )<br>(t <sub>0</sub> ) | )) | and | )<br>Equation 3.3.1                    |

|--------|------------|-----|------------------|----------------|----------|----------|--------|----------------------------------------|----|-----|----------------------------------------|

| u      | э          | (   | U <sub>1</sub> , | U <sub>2</sub> | , .      |          |        | U <sub>n</sub>                         | )) | ,   | an given so sub-                       |

| 5      | =          | (   | s <sub>1</sub> , | S              | , .      |          | •      | s <sub>m</sub>                         | )) |     | bo boosed open .<br>bg. 3.1.13 bus the |

(see section 2.2.2).

where

It will now be suggested that sub-system models can be constructed in one of two ways:

a) by retaining the information contained in

Eq. 3.3.1; in this case the model may be mapped into a logical network, containing a set of logical gates, each representing a simple logical connective. This new network is equivalent to the original sub-system by the definition of equivalence given in Chapter 2.

b) by reducing the information in Eq. 3.3.1,

restricting either the domain of the environment or the admissible time functions of inputs. Using such restrictions Eq. 3.3.1 degenerates to some new form

$$z^{*}(t) = G^{*}(u(t), S(t_{0}))$$

$$z^{*}(t) = H^{*}(u(t), S(t_{0}))$$

Eq. 3.3.2

The sub-routine may now express Eq. 3.3.2 in a form which does not necessarily lend itself to mapping into a logical network. Equation 3.3.2 and its sub-routine version will be termed restricted mode models of the sub-system.

Restricted mode models represent a homomorphic transformation between the systems described by Equations 3.3.1 and 3.3.2. If the sub-system should be subjected to environmental conditions outside of the range of Equation 3.3.2 then the sub-routine model fails. Such in-admissible conditions may easily arise if, for instance, the objects surrounding the sub-system contain some design error. notwithstanding

It will be concluded that/the commendation given to subroutine models in the previous section, such models must be handled with extreme care. Not only must the sub-routine be based upon completely reliable analysis data (as contained in Eq. 3.3.1) but the environment must also be kept under constant observation to ensure the validity of the model.

#### Timing.

The timing description of a system object seeks to define the mapping of time functions performed by the object. While in practice this mapping is extremely complicated due to the nonlinear characteristics of switching circuits, these characteristics could only be observed by resolving the system to higher levels than a logical gate. Alternatively, accepting the single gate as the object at the highest level, as suggested in section 3.3.1, one must accept relatively crude models of objects, such as, for instance, a perfect (delay-free) logical gate, followed by a lumped constant delay.

Some simulators offer facilities for more refined models. The fundamental weakness of these models lies in the absence of reliable information upon which they are based. Device manufacturers are unable to measure the characteristics of some of their devices, or find it uneconomic to measure the characteristics of others. In any case, these characteristics would vary so greatly with the choice of hardware that a common set of parameters may not be easy to find. Hence simulation programs must rely upon crude guesses of timing information and the accuracy of the analysis will not be improved by the use of sophisticated models whose parameters are based on further crude guesses.

The most commonly used time model is, as mentioned, a propagation delay  $t_p$ , associated with each object output. Some simulators permit the use of two time parameters  $t_pr$  and  $t_pr$ , representing the time delay associated with rise and fall, respectively.

A more sophisticated time model adds a further threshold delay  $t_t$  which demands that the input signal pulse should be ignored unless the duration of the pulse exceeds  $t_t$ .

It is reported that an industrial research group is seeking to develop a time model which would incorporate non-constant time parameters. Dependent upon the amount of load supplied by an object output, different values of  $t_p$  and  $t_t$  would now be assigned to the same system object. This project suffers from the same lack of reliable time data as has been mentioned before.

A far more ambitious project is reported (29) by members of the IBM corporation. The work of this group concerns the development of a statistical delay model for a simple logical network. The model correlates the variation of some physical signals and of load with the time delay of gates. Such is the complexity of this problem that it was necessary to construct a purpose-built computer system to carry out data collection and processing, while calculations were performed on an IBM 7044. In spite of the extravagant resources used by the project, the results have very limited practical application.

The uncertainty of time data emerges as a fundamental shortcoming of simulation as a practical mode of analysis of logical networks. By the definition of simulation, verification of designs is based upon observing the system response in the time domain, but this response is computed on the basis of crude models whose parameters are derived by wild guessing.

#### 3.3.3 - Input data.

Fixing the highest resolution level at gate level implies that operating signals should be modelled by discontinuous jumps between two logical levels. The specification of these operating signals consists of the listing of those instances of time when a given operating signal is scheduled to change. As an aid to coding of this data, some simulators permit the use of oscillators in addition to switches. The oscillators provide periodically changing signals whose ON and OFF time may be specified.

Physical signals (supply potentials, temperature) are considered as constant and, as mentioned in the previous section, their effect upon the time delays associated with object outputs is neglected.

The sample space is thus restricted to dimensions given by the operating signals and state variables. Even so, this space is excessively large for all but trivial networks. The number of necessary steady-state and transient tests will be assessed in chapter 4. It will be sufficient to mention a few problems arising at coding.

The simulation commences by the specification of an initial state. In the absence of such specification simulators assume that all state variables are to be set at, say, logical '0'. If this condition is logically inconsistent (unstable) then a series of calculations commences while the simulator searches for a steady state of the system. This may not always be found, or not found within the time limit set by the designer. In such a case the simulator refuses the network (as in the case of the RACAL program) or over-writes a transient state by permitting the operating signal sequence to begin (such as in case of the LOGIC program). Neither of these solutions is particularly attractive: one refuses to simulate the system altogether while the other may give ambiguous results depending upon a random choice between oscillatory states.

If the initial state selected by the designer or set up by the program is not connected to some of the system states then no finite time sequence of operating signals would result in a comprehensive analysis.

Oscillator-driven inputs imply a restricted mode of analysis. While it is possible to construct oscillator signals which permit the system to be tested for all of the 2<sup>n</sup> number of different input signal combinations for n inputs, this number of tests subjects the system to only a small fraction of the total number of different transient conditions and will only ascertain the response in the case of the selected initial state. The solution is sought by selecting sequences of operating signal changes which are regarded by the designer as most probable to occur. For instance, it is often found that networks are simulated under conditions when an output is scheduled to generate a specific signal. If the network passes the test, then the designer assumes that the design is correct. This assumption is fallatious because it is based on the same value judgement as was used by the designer when proposing the design. The network may behave incorrectly by generating outputs at untested conditions.

An alternative method is to select input sequences entirely at random. This way there is a probability of selecting conditions which might have been overlooked at the design stage. Even so, it is very difficult to assign a significance level to a selected test sequence and the reliability of the analysis is in doubt.

The problems discussed here are familiar from experience with hardware testing and there is no evidence that the newly developed

techniques of computer simulation offer a satisfactory solution. 3.3.4 - Input - Output Mapping.

The process of computer simulation of logical networks consists of specifying the changes of input signals in the time domain and following the passage of signal changes through the network. The procedure demands the choice of time quanta at the input and throughout the operation of the network.

<u>Synchronous simulation</u> refers to a system in which time is incremented by equal intervals and the model is processed at each time increment. Inputs and outputs are shown on a linear time scale, with a line of print assigned to each increment.

<u>Asynchronous simulation</u> is frequently termed "next event" or "event-by-event" simulation, indicating that time is incremented by periods measuring the distance between subsequent events, either at the input or within the network.

The printout of event-by-event simulators show input and output waveforms on a non-linear time scale, with a line of print assigned to each event, against a parameter of time.

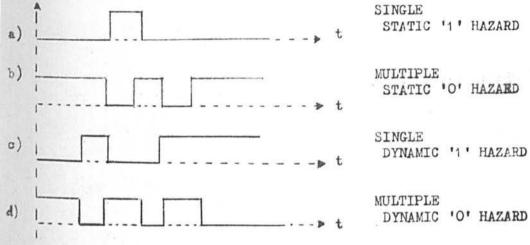

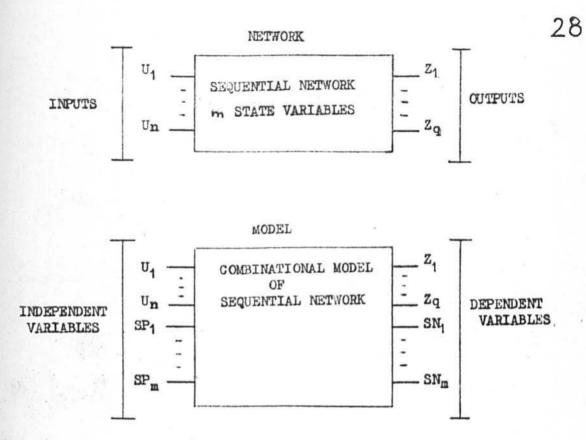

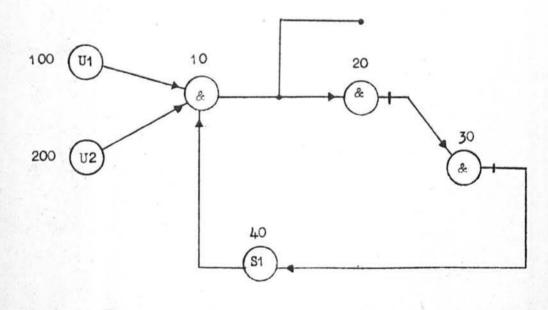

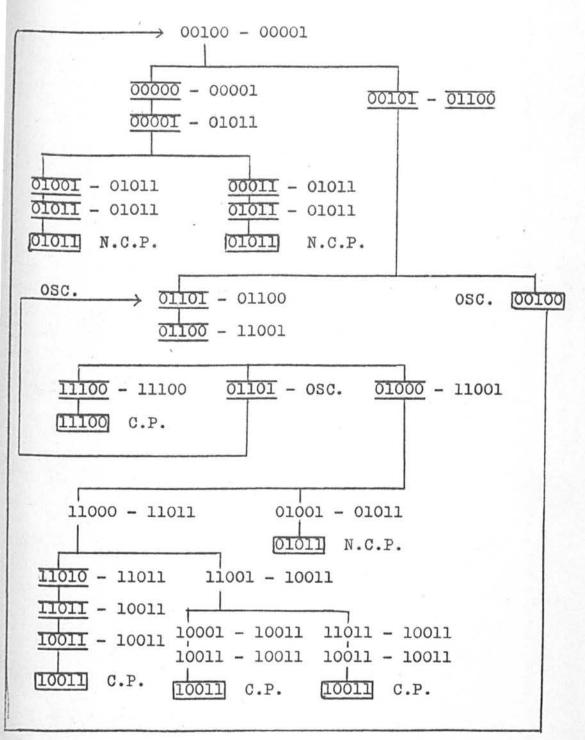

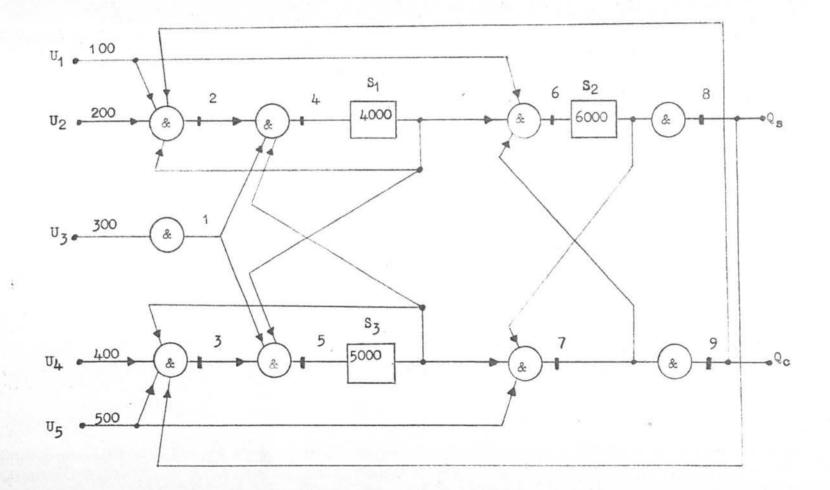

Asynchronous simulators offer flexibility; they lend themselves to the analysis of synchronous or asynchronous networks. Most of the known simulators are asynchronous.